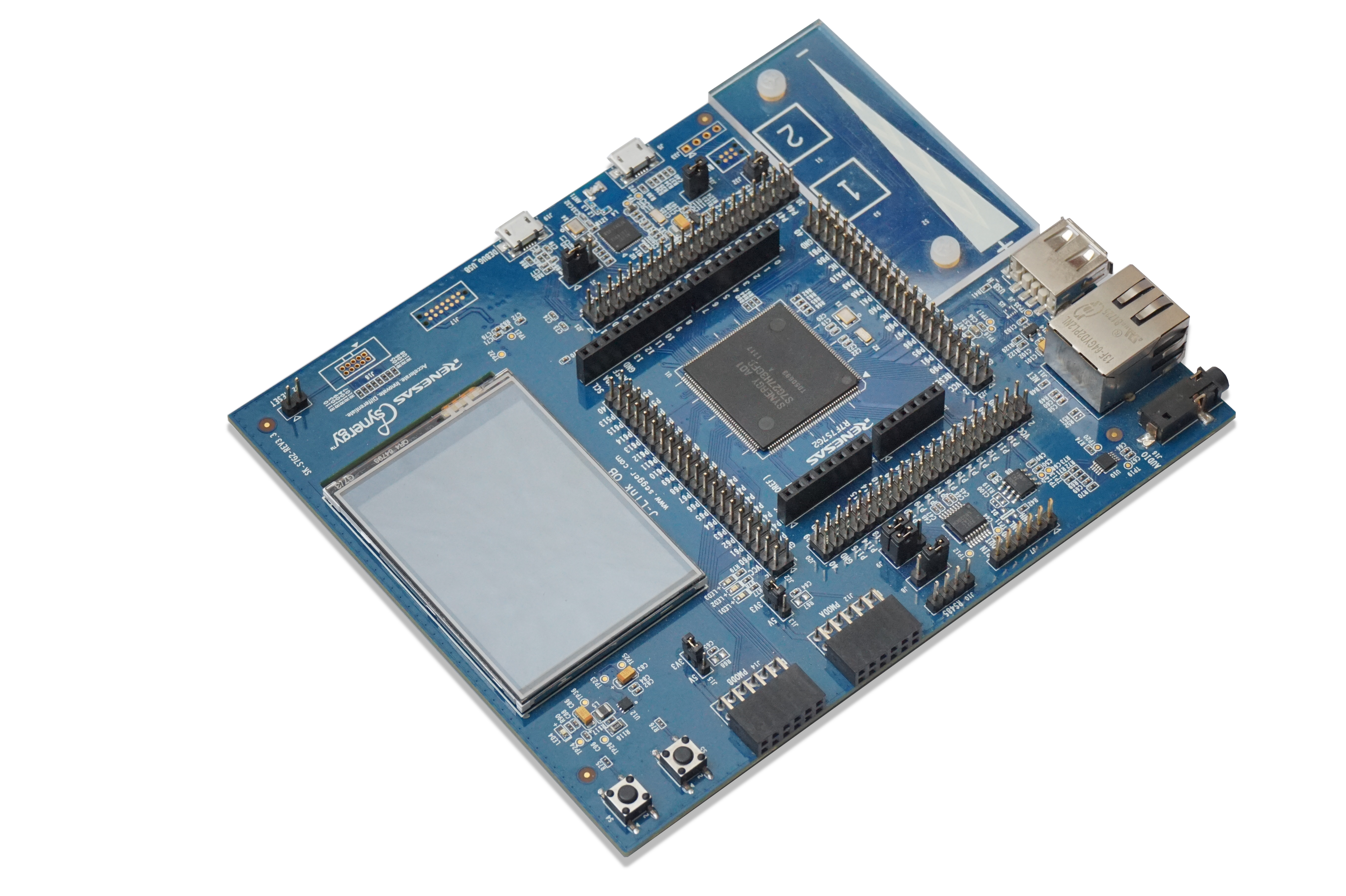

The Renesas Synergy S7G2-SK is a development board of the manufacterer Renesas. The device is a 240 MHz Arm® Cortex®-M4 CPU with up to 4 MB of flash memory and 640 KB of SRAM. It is capable as an application controller for the iRJ45/SoM module.

The e2 studio by Renesas is a free Integrated Development Environment which provides several utilities to develope and debug applications for the Synergy S7G2-SK. It is available on the Renesas website. The appropriate Synergy Software Package, which contains a code generator and several libraries is also availiable on the website.

For compiling the example code, the GNU Arm Embedded Toolchain is required. It can be obtained in several ways. Further information can be found here: https://developer.arm.com/tools-and-software/open-source-software/developer-tools/gnu-toolchain/gnu-rm/downloads. To flash the application the J-Link Software pack is needed.

Make sure, the toolchain and Jlink Software Directory is added properly to your path variable after the installation. |

Make sure following settings are set:

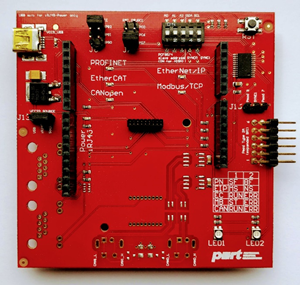

J13 - Connect “iRJ45” with “Sockel”

J8 - Connect “CS_SOURCE” with “PB2”

J7 - Connect “RST_SOURCE” with “PD7”

Set all DIP-Switches to “OFF”

Per default there are no jumpers to set on this board.

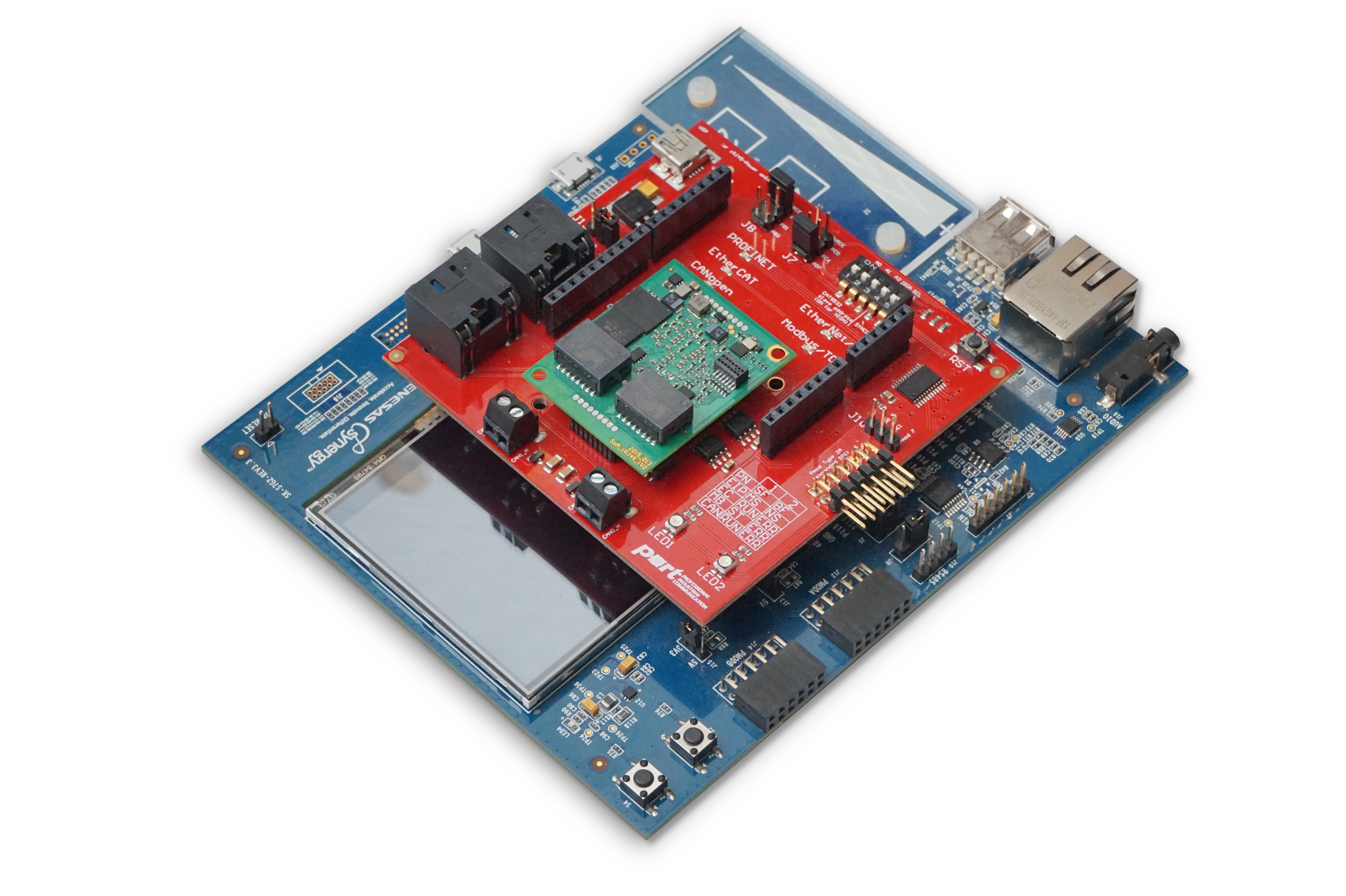

Connect both boards (see Figure above). Voltage supply is done through the VCC33_Sockel by the Synergy S7G2-SK.

Please connect both boards with each other, before you connect them per USB to your computer. |

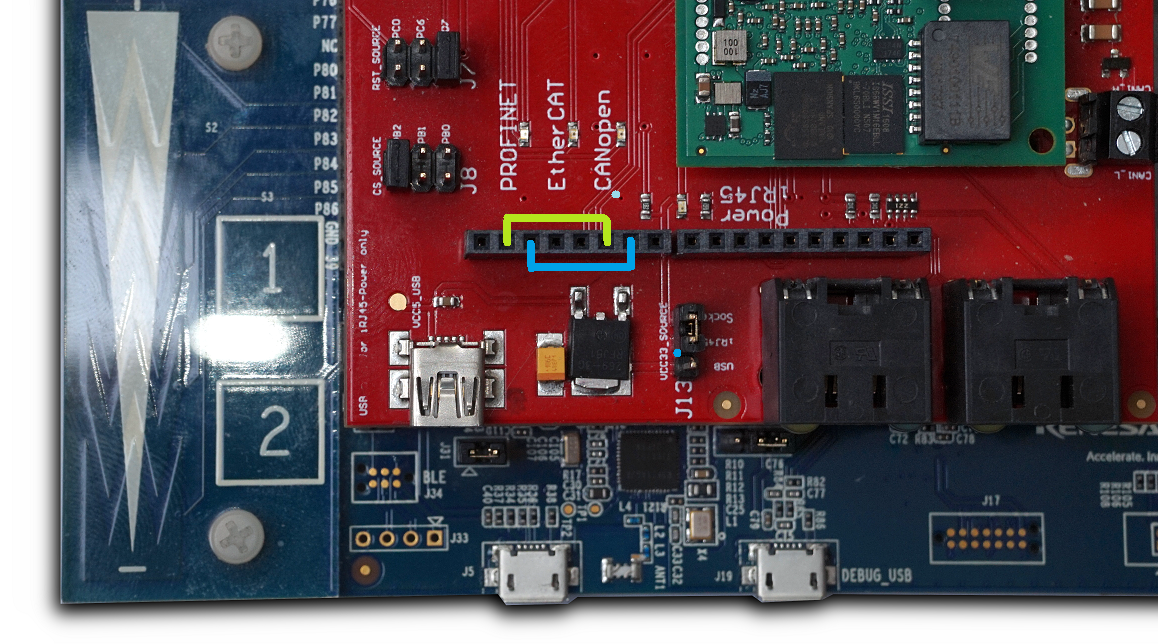

The Platform Renesas Synergy S7G2-SK supports the feature EtherCAT Distributed Clocks (DC). The synchronization signal SYNC0 and SYNC1 from the SoM are connected through the Arduino Adaptershield to the Renesas Synergy S7G2-SK. To use the signals a bridge is needed to connect the pins 7 and 4 of the Arduino Adaptershield. Connected as shown in the figure below, both of the SYNC signals cause an interrupt on the Renesas Synergy S7G2-SK.

Within a example folder “ugoal/projects/ugoal/<example name>/gcc” of the software delivery, build the firmware with following commands:

make PLATFORM=s7g2sk |

Use following command within the example folder, to flash the application onto the Synergy S7G2-SK:

make PLATFORM=s7g2sk flash |

The Jlink Software directory must be added to the path variable, otherwise the build system won’t be able to flash the device. |

If you want to clean the build, use following command:

make PLATFORM=s7g2sk clean |

This chapter describes the integration of the source files into a new e2 studio project, to edit, compile and debug the software delivery.

From any project folder a project generator can be run to create an e2 studio project for the application. The project generator requires a python3 installation. Required dependencies are installed automatically.

If you want to create a e2 studio project, run the following command:

make PLATFORM=s7g2sk gen_project Please select a template - OR - press <CTRL+c> and set the GEN_PROJECT_TPL environment variable. Choose IDE: [ 1] e2studio [ 2] eclipse [ 3] mcuxpressoide [ 4] stmcubeide Choice [1-4]: |

For Renesas Synergy S7G2-SK the template number 2 needs to be chosen.

Selected template: [2] e2studio/renesas/s7g2sk gen_project ----------- Project: 02_profinet_s7g2sk Templates: /home/tbi/2015013_irj45/ugoal/tools/gen_project/templates/e2studio/renesas/s7g2sk Generating: .cproject .project configuration.xml S7G2-SK.pincfg com.renesas.cdt.managedbuild.gnuarm.prefs com.renesas.cdt.synergy.contentgen.prefs com.renesas.cdt.synergy.packs.componentfiles.prefs com.renesas.cdt.synergy.settingseditor.prefs com.renesas.cdt.synergy.threads.configurator.prefs language.settings.xml org.eclipse.cdt.codan.core.prefs org.eclipse.cdt.core.prefs cgprojectDatas.datas r7fs7g27h3a01cfc.ld hal_entry.c Output dir: /home/tbi/2015013_irj45/ugoal/projects/ugoal/02_profinet/gcc/../ide/e2studio/renesas/s7g2sk/ |

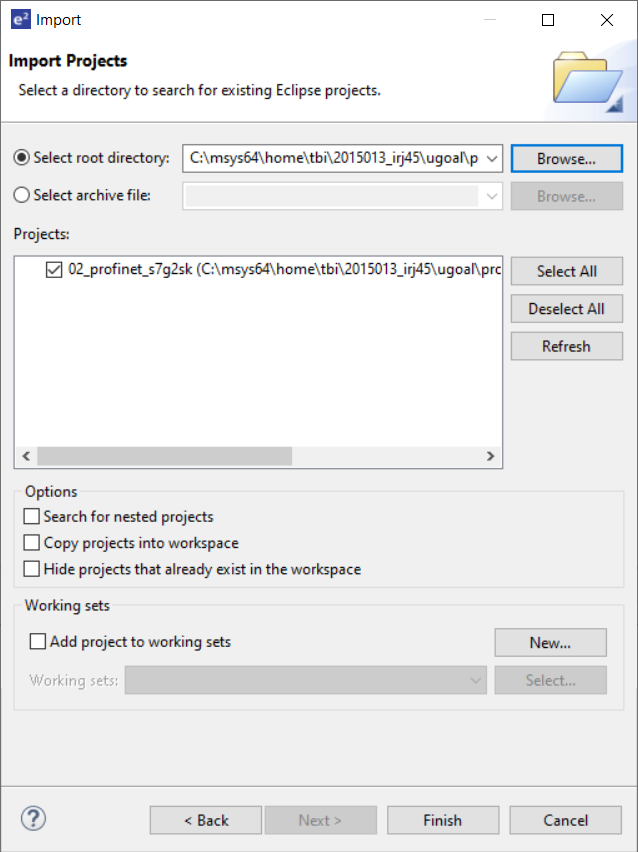

The generated project should be imported into e2studio using “Import → Existing Projects into Workspace” and be browsing to the project folder:

Older windows versions limit path length to 256 bytes. Thus please make sure that the project path doesn’t exceed this limit. |

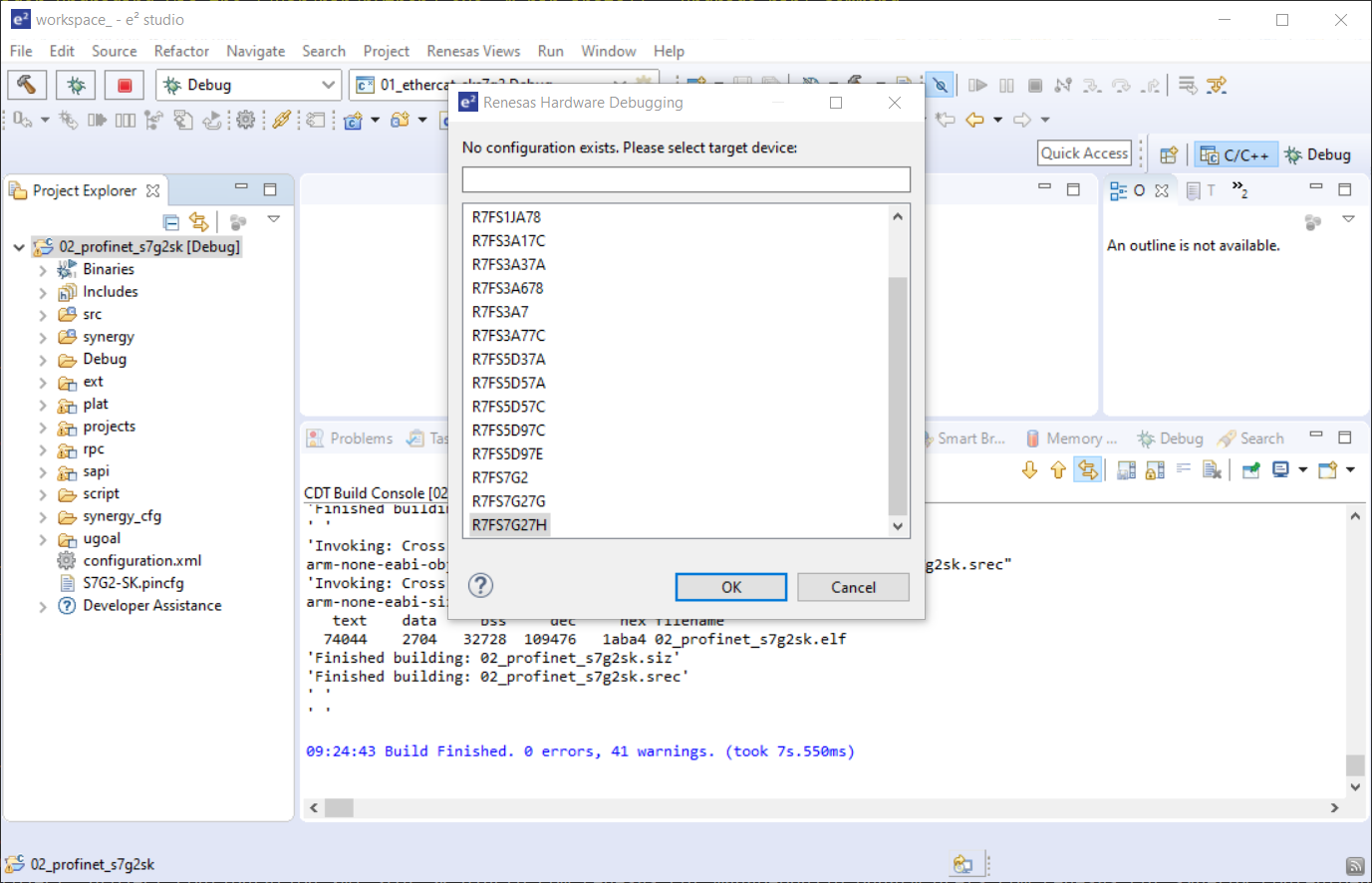

The imported project can be build and debugged via “Debug As → 3 Renesas GDB Hardware Debugging“. Choose select the target device “R7FS7G27H”.

The UART-interface of the Renesas Synergy S7G2-SK is accessable through the J10 connector. Please set jumper J9 to 3-5 and 4-6 (RS485 mode). Then the UART TX line from the Synergy CPU will be connected to Pin 4 of J10. This is where the RX line from the USB-Serial converter needs to be connected. You can access the UART by launching a serial monitor like putty. Choose the following settings:

Speed | 115200 |

Data Bits | 8 |

Stop Bits | 1 |

Parity | None |

Flow Control | XON/XOFF |

After setting up the serial monitor and starting the application, the output should look like this:

[INF] ugoal/rpc/wrapper/pnio/goal_pnio_rpc_ac.c:341 PROFINET Application Core successfully started [INF] ugoal/projects/ugoal/02_profinet/goal_appl.c:250 Initializing device structure [INF] ugoal/rpc/wrapper/pnio/goal_pnio_rpc_ac.c:4130 generic data provider mapped to position 0 [INF] ugoal/projects/ugoal/02_profinet/goal_appl.c:307 PROFINET ready [INF] ugoal/rpc/goal_media/goal_mi_mctc.c:506 local setup done [INF] ugoal/ugoal.c:288 HEAP utilization: 3624/24576 (14%). [INF] ugoal/plat/s7g2sk/plat.c:187 !! application setup done !! |

Currently there are no known restrictions.